# 2N4340, 2N4341 N-Channel JFET

### Features

- InterFET <u>N0016H Geometry</u>

- Low gate leakage: < 1pA typical @40V</li>

- Low Ciss: 3pF typical

- Typical noise: 3.5 nV/VHz

- Typical gain: 2mS

- Typical cutoff voltage: -2.5V

- High radiation tolerance

- RoHS, REACH, CMR compliant

- · Custom test and binning options available

- SMT, TH, and bare die package options

- Edge case SPICE modeling: InterFET SPICE

### Industry Standard Crosses

- 2SK40, 2SK105, SST202

- 2N4868A, 2N4869A, 2N4221A, J231, J202, VCR4N

#### **InterFET Similar Parts**

- IFN202, IFN160C, IFN105, IFN40, SMPVCR4N

- SMP4868A, SMP4869A, SMP4221A, SMPJ232

### **InterFET Dual Parts**

- IFNU231, IFNU232, IFNU233, IFNU234, IFNU235

- IFN5197, IFN5198, IFN5199, IFNU410, IFNU411, IFNU412

- IFNU401, IFNU402, IFNU403, IFNU404, IFNU405, IFNU406

## Applications

- General: Amplifiers; Switches; Voltage regulators; Oscillators; Signal mixers; Noise generators

- Military/Aero: Radar; Communications; Satellites; Missiles guidance; Hydrophone preamplifiers

- Medical: Medical imaging systems; Medical monitors and recorders; Ultrasound equipment

- Audio: Tone control circuits; Headphone amplifiers; Audio filters; Electret Microphone

### Description

The -50V InterFET 2N4340 and 2N4341 are very low leakage mid-gain JFETs targeted for sensitive amplifier stages for mid-frequencies designs. Gate leakages are less than 1pA at room temperatures. Proprietary InterFET processes yield exceptionally high radiation tolerance.

| Part Number                                                          | Description                            | Case            | Packaging            |  |

|----------------------------------------------------------------------|----------------------------------------|-----------------|----------------------|--|

| 2N4340; 2N4341                                                       | Through-Hole                           | TO-18           | Bulk                 |  |

| PN4340; PN4341                                                       | 4340; PN4341 Through-Hole TO-92 E      |                 | Bulk                 |  |

| SMP4340; SMP4341                                                     | Surface Mount                          | SOT23           | Bulk                 |  |

|                                                                      | 7" Tape and Reel: Max 3,000 Pieces     |                 | Minimum 1,000 Pieces |  |

| SMP4340TR; SMP4341TR                                                 | 13" Tape and Reel: Max 9,000 Pieces    | SOT23           | Tape and Reel        |  |

| 2N4340COT; 2N4341COT                                                 | Chip Orientated Tray (COT Waffle Pack) | СОТ             | 400/Waffle Pack      |  |

| N4340CFT; 2N4341CFT Chip Face-up Tray (CFT Waffle Pack) CFT 400/Waff |                                        | 400/Waffle Pack |                      |  |

#### Ordering Information Custom Part and Binning Options Available

NOTICE: Please refer to the end of this document for information on product materials, compliance, safety, and legal statements.

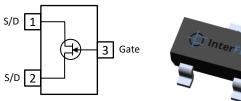

NOTE: S/D pins are interchangeable Source Drain connections

# **Electrical Characteristics**

## Maximum Ratings (@ T<sub>A</sub> = 25°C, Unless otherwise specified)

|                  | Parameters                                       | TO-18      | SOT-23     | TO-92      | Unit  |

|------------------|--------------------------------------------------|------------|------------|------------|-------|

| V <sub>RGS</sub> | Reverse Gate Source and Gate Drain Voltage       | -30        | -30        | -30        | V     |

| IFG              | Continuous Forward Gate Current                  | 50         | 50         | 50         | mA    |

| PD               | Continuous Device Power Dissipation <sup>1</sup> | 500        | 350        | 500        | mW    |

| Р                | Power Derating <sup>1</sup>                      | 3.3        | 2.8        | 4          | mW/°C |

| Tj               | Operating Junction Temperature                   | -65 to 175 | -55 to 150 | -55 to 150 | °C    |

| Tstg             | Storage Temperature                              | -65 to 175 | -55 to 150 | -55 to 150 | °C    |

<sup>1</sup> Thermal power dissipation and derating values obtained with gate pin (substrate) thermally connected to pad and/or internal layer.

#### Static Characteristics (@ TA = 25°C, Unless otherwise specified)

|                      | 2N4340                                |                                                                                                                                             | 340 | 2N4341       |     |               |         |

|----------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|-----|---------------|---------|

|                      | Parameters                            | Conditions                                                                                                                                  | Min | Max          | Min | Max           | Unit    |

| V(BR)GSS             | Gate to Source<br>Breakdown Voltage   | V <sub>DS</sub> = 0V, I <sub>G</sub> = -1μΑ                                                                                                 | -50 |              | -50 |               | v       |

| I <sub>GSS</sub>     | Gate to Source<br>Reverse Current     | V <sub>GS</sub> = -30V, V <sub>DS</sub> = 0V, T <sub>A</sub> = 25°C<br>V <sub>GS</sub> = -30V, V <sub>DS</sub> = 0V, T <sub>A</sub> = 150°C |     | -0.1<br>-100 |     | -0.1<br>-100  | nA      |

| V <sub>GS(OFF)</sub> | Gate to Source<br>Cutoff Voltage      | V <sub>DS</sub> = 15V, I <sub>D</sub> = 0.1µA                                                                                               | -1  | -3           | -2  | -6            | V       |

| I <sub>DSS</sub>     | Drain to Source<br>Saturation Current | $V_{GS} = 0V, V_{DS} = 15V$<br>(Pulsed)                                                                                                     | 1.2 | 3.6          | 3   | 9             | mA      |

| Id(off)              | Drain Cutoff Current                  | $V_{DS} = 15V, V_{GS} = ()$                                                                                                                 |     | 0.05<br>(-5) |     | 0.07<br>(-10) | nA<br>V |

## Dynamic Characteristics (@ TA = 25°C, Unless otherwise specified)

|                     |                                  | 2N4340                                                                      |      | 340  | 2N4341 |      |      |

|---------------------|----------------------------------|-----------------------------------------------------------------------------|------|------|--------|------|------|

|                     | Parameters                       | Conditions                                                                  | Min  | Max  | Min    | Max  | Unit |

| GFS                 | Forward<br>Transconductance      | V <sub>DS</sub> = 15V, V <sub>GS</sub> = 0V, f = 1kHz                       | 1300 | 3000 | 2000   | 4000 | μS   |

| Gos                 | Output<br>Conductance            | V <sub>DS</sub> = 15V, V <sub>GS</sub> = 0V, f = 1kHz                       |      | 30   |        | 60   | μS   |

| R <sub>DS(ON)</sub> | Drain to Source<br>ON Resistance | $V_{GS}$ = 0V, $I_D$ = 0A, f = 1kHz                                         |      | 1500 |        | 800  | Ω    |

| Ciss                | Input Capacitance                | V <sub>DS</sub> = 15V, V <sub>GS</sub> = 0V, f = 1MHz                       |      | 7    |        | 7    | pF   |

| Crss                | Reverse Transfer<br>Capacitance  | $V_{DS}$ = 15V, $V_{GS}$ = 0V, f = 1MHz                                     |      | 3    |        | 3    | pF   |

| NF                  | Noise Figure                     | $V_{DS} = 15V, V_{GS} = 0V, f = 1kHz$<br>R <sub>G</sub> = 1 MΩ, BW = 200 Hz |      | 1    |        | 1    | dB   |

Order Now

Technical

Support

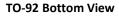

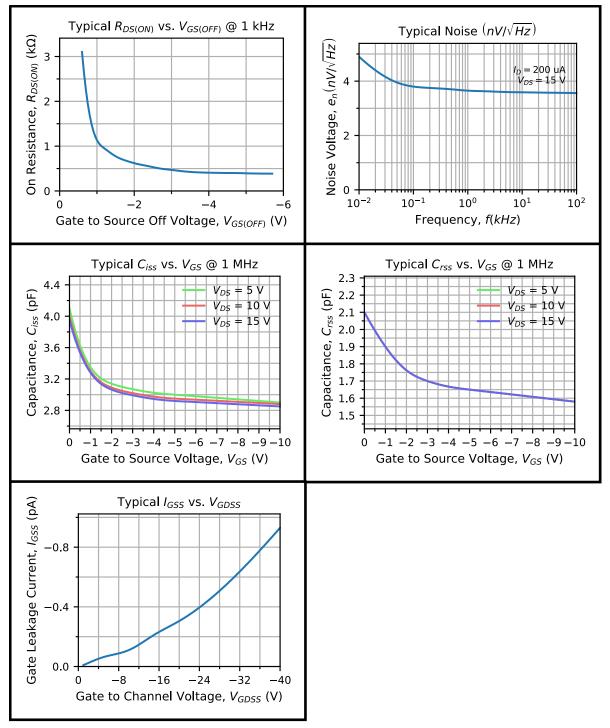

# Typical 2N4340, 2N4341 Characteristics

Order Now

Technical

Support

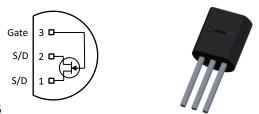

# Typical 2N4340, 2N4341 Characteristics (Continued)

Technical

Support

Order

Now

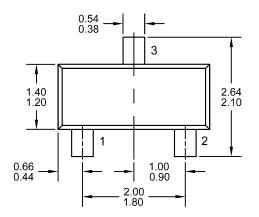

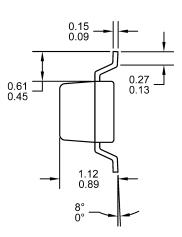

# SOT23 (TO-236AB) Mechanical and Layout Data

### Package Outline Data

## Suggested Pad Layout

- 1. All linear dimensions are in millimeters.

- 2. Package weight approximately 0.12 grams

- 3. Molded plastic case UL 94V-0 rated

- For Tape and Reel specifications refer to InterFET CTC-021 Tape and Reel Specification, Document number: IF39002

- 5. Bulk product is shipped in standard ESD shipping material

- 6. Refer to JEDEC standards for additional information.

- 1. All linear dimensions are in millimeters.

- 2. The suggested land pattern dimensions have been provided for reference only. A more robust pattern may be desired for wave soldering.

Order

Now

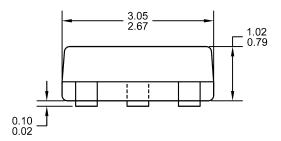

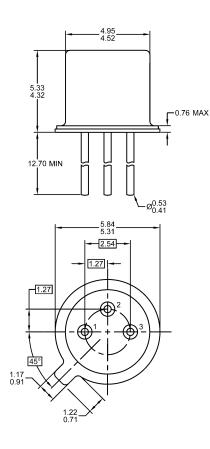

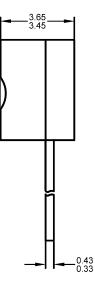

# **TO-18 Mechanical and Layout Data**

### **Package Outline Data**

## Suggested Through-Hole Layout

- 1. All linear dimensions are in millimeters.

- 2. Package weight approximately 0.29 grams

- 3. Bulk product is shipped in standard ESD shipping material

- 4. Refer to JEDEC standards for additional information.

- 1. All linear dimensions are in millimeters.

- 2. The suggested land pattern dimensions have been provided as a straight lead reference only. A more robust pattern may be desired for wave soldering and/or bent lead configurations.

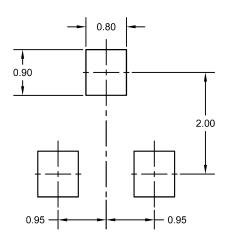

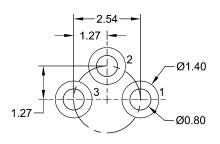

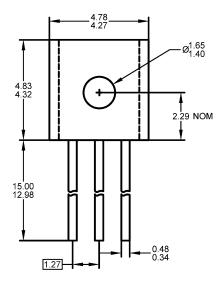

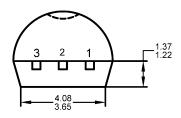

# **TO-92 Mechanical and Layout Data**

# Package Outline Data

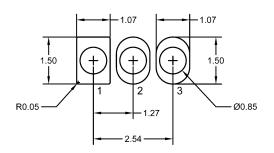

# Suggested Through-Hole Layout

- 1. All linear dimensions are in millimeters.

- 2. Package weight approximately 0.19 grams

- 3. Molded plastic case UL 94V-0 rated

- 4. Bulk product is shipped in standard ESD shipping material

- 5. Refer to JEDEC standards for additional information.

- 1. All linear dimensions are in millimeters.

- 2. The suggested land pattern dimensions have been provided as a straight lead reference only. A more robust pattern may be desired for wave soldering and/or bent lead configurations.

# **Compliance and Legal**

#### Environment

InterFET parts follow the latest RoHS Compliance, REACH Compliance, Proposition 65 Statement, TSCA Statement, and Chemical Disposal and Waste Mitigation requirement and guidelines. For more on InterFET's Environmental Commitment please visit www.InterFET.com/environmental/.

Technical

Support

#### **Package materials**

| Parameters | SOT23         | SOIC8         | TO-92         | Metal Case |

|------------|---------------|---------------|---------------|------------|

| Alloy      | CDA194        | C194 1/2H     | C194 1/2H     | Kovar      |

| Cu         | Balance       | 97% min       | 97% min       |            |

| Fe         | 2.1 - 2.6%    | 2.1 - 2.6%    | 2.1 - 2.6%    | 53%        |

| Zn         | 0.05 – 0.2%   | 0.05 – 0.2%   | 0.05 - 0.15%  |            |

| Р          | 0.015 - 0.15% | 0.015 - 0.15% | 0.015 - 0.15% |            |

| Pb         | 0.03% max     | 0.03% max     | 0.03% max     |            |

| Ni         |               |               |               | 29%        |

| Со         |               |               |               | 17%        |

| Mn         |               |               |               | 0.3%       |

| Si         |               |               |               | 0.2%       |

| С          |               |               |               | <0.01%     |

| Au         |               |               |               | Plating    |

#### **Package tests**

| Parameters SOT23 |                                        | SOIC8                                  | TO-92                                  | Metal Case                             |  |

|------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--|

| MSL              | Level 1                                | Level 1                                | N/A                                    | N/A                                    |  |

| ESD              | Class M4 Machine Model<br>Class 3A HBM |  |

## Legal Notice

InterFET Corporation reserves the right to make corrections, enhancements, improvements, modifications, and other changes to its semiconductor products without further notice to this document and any product described herein. InterFET does not assume any liability arising out of the application or use of this document or any product described herein. Unless InterFET has explicitly designated an individual product as meeting the requirements of a particular industry standard, InterFET is not responsible for any failure to meet such industry standard requirements.

InterFET Corporation assumes no liability for a customers product design or applications. Corporate designers and others who are developing systems that incorporate InterFET products understand and agree that they remain responsible for using their independent analysis, evaluation and judgment in designing their applications. Corporate designers and others have full and exclusive responsibility to assure the safety of Designers' applications and compliance of their applications with all applicable regulations, laws and other applicable requirements.

InterFET Corporation resources are provided "as is" with potential faults. InterFET disclaims all other warranties or representations, express or implied, regarding resources or use thereof, including but not limited to accuracy or completeness, title, any widespread failure warranty and any implied warranties of merchantability, fitness for a particular purpose, and non-infringement of any third party intellectual property rights. InterFET shall not be liable for and shall not defend or indemnify designer against any claim, including but not limited to any infringement claim that relates to or is based on any combination of products even if described in InterFET resources or otherwise. In no event shall InterFET be liable for any actual, direct, special, collateral, indirect, punitive, incidental, consequential or exemplary damages in connection with or arising out of InterFET resources or use thereof, and regardless of whether InterFET has been advised of the possibility of such damages.