## CGD65B200S2 DATASHEET

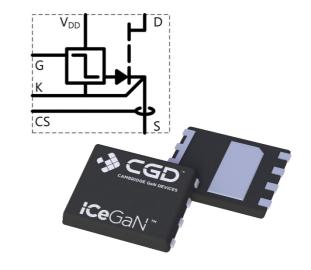

650 V / 200 mΩ GaN HEMT with ICeGaN™ Gate and Current Sense

DECEMBER 2022

# 650 V / 200 mΩ GaN HEMT with ICeGaN™ Gate and Current Sense

#### **Key features**

- 650 V 8.5 A e-mode GaN power switch

- ICeGaN™ gate technology for high gate threshold and broad gate voltage window compatible with gate-drivers and controllers for Si MOSFETs

- Gate drive voltage 9 V to 20 V

- Current sense function

- $R_{DS(on)} = 200 \text{ m}\Omega$

- Suitable for very high switching frequency

- Kelvin Contact

- Small 5x6 mm<sup>2</sup> PCB footprint

- Bottom side cooled DFN package

#### **Description**

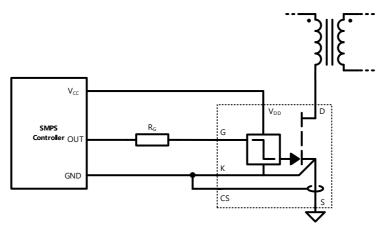

The CGD65B200S2 is an enhancement mode GaN-on-silicon power transistor, exploiting the unique material properties of GaN to deliver high current, high breakdown voltage and high switching frequency for a wide range of electronics applications. The CGD65B200S2 features CGD's ICeGaN™ gate technology enabling compatibility with virtually all gate drivers and controller chips available. The integrated current sense function eliminates a separate current sense resistor and the associated efficiency losses. Because no external sense resistor is needed, the device can be directly soldered to the large copper area of the ground plane, improving the thermal performance and simplifying the thermal design. It comes in a DFN 5x6 SMD package to support high frequency operation while ensuring the highest thermal performance.

#### **Application & Topologies**

PSUs, Industrial SMPS and inverters

- Mobile chargers, fast-chargers

- AC adapters

- Notebook adapters, PC power

- Gaming PSUs

- LED lighting

- Class-D Audio

- TV and wireless power

- PV micro-inverters

- SMPS and converters in single-switch and halfbridge topologies with hard- or soft-switching

- DC/DC converters

- Quasi-resonant flyback and Active Clamp flyback

- Totem pole and single-switch PFC

- LLC and high frequency converters

- Class-E inverters

Figure 1. Exemplary Application Circuit

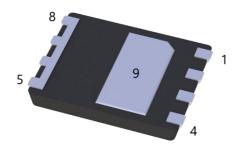

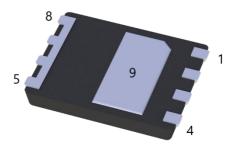

| PIN | NAME            | DESCRIPTION                                                                             |  |

|-----|-----------------|-----------------------------------------------------------------------------------------|--|

| 1   | Kelvin Source   | Kelvin source connection (internally tied to power HEMT source), reference              |  |

|     |                 | potential for gate voltage.                                                             |  |

| 2   | Gate            | Gate signal input.                                                                      |  |

|     |                 | Recommended gate-drive voltage: $V_{drive}$ ( $V_{GS}$ in on-state) = 9 V to $V_{DD}$ . |  |

| 3   | Current Sense   | Current sense output, relative to source, non-isolated.                                 |  |

| 4   | V <sub>DD</sub> | ICeGaN™ gate supply voltage (recommended at 12 V), relative to source.                  |  |

| 5-8 | Drain           | Power HEMT drain                                                                        |  |

| 9   | Source          | Power HEMT source, thermal pad                                                          |  |

Figure 2. Pin Configuration and Functions

#### **Absolute Maximum Ratings**

$T_{case}$  = 25 °C if not listed.

| PARAMETER                                            |                            | VALUE                                 | UNIT |

|------------------------------------------------------|----------------------------|---------------------------------------|------|

| Operating Junction Temperature                       | TJ                         | -55 to +150                           | °C   |

| Storage Temperature Range                            | Ts                         | -55 to +150                           | °C   |

| Drain-to-Source Voltage                              | V <sub>DS</sub>            | 650                                   | V    |

| Drain-to-Source Voltage - transient <sup>1</sup>     | V <sub>DS(transient)</sub> | 750                                   | V    |

| Gate-to-Source Voltage                               | V <sub>GS</sub>            | -1 to +20                             | V    |

|                                                      |                            | and V <sub>GS</sub> ≤ V <sub>DD</sub> |      |

| Gate-to-Source Voltage - transient <sup>2</sup>      | V <sub>GS(transient)</sub> | -1.5 to +21.5 and                     | V    |

|                                                      |                            | $V_{GS} \leq V_{DD} + 1.5$            |      |

| Current Sense Voltage                                | V <sub>CS</sub>            | -1.5 to 1.5                           | V    |

| ICeGaN™ Gate Supply Voltage                          | $V_{DD}$                   | 0 to +20                              | V    |

| Continuous Drain Current (T <sub>case</sub> = 25 °C) | I <sub>D</sub>             | 8.5                                   | Α    |

The recommended range of operation for  $V_{drive}$  ( $V_{GS}$  in on-state) and  $V_{DD}$  is 9 V to 20 V, enabling simple integration with a large variety of control chips and gate drivers.

Recommended maximum operating case temperature: T<sub>case</sub> = 125 °C.

$<sup>^{1}</sup>$  Non-repetitive pulsed conditions, < 1 ms.

$<sup>^{\</sup>rm 2}$  Non-repetitive pulsed conditions.

#### **Electrical Characteristics**

Values at  $T_J = 25$  °C,  $V_{DD} = 12$  V if not listed. To turn the device on the recommended gate voltage range is  $V_{GS} = 9$  V to  $V_{DD}$ . To turn the device off set  $V_{GS} = 0$  V. An integrated Miller Clamp eliminates the need for negative gate voltages.

#### **STATIC CHARACTERISTICS**

| PARAMETER                        |                     | CONDITIONS                                        | MIN | TYP | MAX | UNIT |

|----------------------------------|---------------------|---------------------------------------------------|-----|-----|-----|------|

| Drain-to-Source Blocking Voltage | BV <sub>DS</sub>    | $V_{GS} = 0 \text{ V}, I_{DSS} = 5.5 \mu\text{A}$ | 650 |     |     | V    |

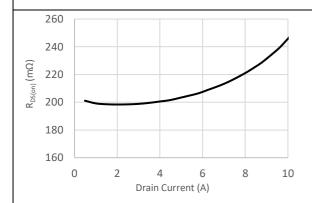

| Drain-to-Source On Resistance    | R <sub>DS(on)</sub> | $V_{GS} = 12 \text{ V}, I_{D} = 0.6 \text{ A}$    |     | 200 | 280 | mΩ   |

| Drain-to-Source On Resistance    | R <sub>DS(on)</sub> | T <sub>J</sub> = 150 °C                           |     | 530 |     | mΩ   |

|                                  |                     | $V_{GS} = 12 \text{ V}, I_D = 0.6 \text{ A}$      |     |     |     |      |

| Source-to-Drain Voltage          | V <sub>SD(on)</sub> | $V_{GS} = 0 \text{ V}, I_{D} = 0.6 \text{ A}$     |     | 2.0 | 3.7 | V    |

| Gate-to-Source Threshold         | V <sub>GS(th)</sub> | $V_{DS} = 0.1 \text{ V}, I_{D} = 2.75 \text{ mA}$ | 2.2 | 2.9 | 4.2 | V    |

| Gate-to-Source Threshold         | V <sub>GS(th)</sub> | T <sub>J</sub> = 150 °C                           |     | 2.6 |     | V    |

|                                  |                     | $V_{DS} = 0.1 \text{ V}, I_{D} = 2.75 \text{ mA}$ |     |     |     |      |

| Gate-to-Source Current           | I <sub>GS</sub>     | $V_{GS} = 12 \text{ V}, V_{DS} = 0 \text{ V}$     |     | 2.8 | 3.7 | mA   |

| Gate-to-Source Current           | I <sub>GS</sub>     | T <sub>J</sub> = 150 °C                           |     | 2.5 |     | mA   |

|                                  |                     | $V_{GS} = 12 \text{ V}, V_{DS} = 0 \text{ V}$     |     |     |     |      |

| V <sub>DD</sub> current          | I <sub>VDD</sub>    | $V_{GS} = 12 \text{ V}, V_{DS} = 0 \text{ V}$     |     | 1.8 | 2.8 | mA   |

| V <sub>DD</sub> current          | I <sub>VDD</sub>    | T <sub>J</sub> = 150 °C                           |     | 1.1 |     | mA   |

|                                  |                     | $V_{GS} = 12 \text{ V}, V_{DS} = 0 \text{ V}$     |     |     |     |      |

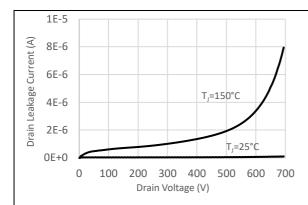

| Drain-to-Source Leakage Current  | I <sub>DSS</sub>    | $V_{GS} = 0 \text{ V}, V_{DS} = 650 \text{ V}$    |     | 0.1 | 5.5 | μΑ   |

| Drain-to-Source Leakage Current  | I <sub>DSS</sub>    | T <sub>J</sub> = 150 °C                           |     | 6   |     | μΑ   |

|                                  |                     | $V_{GS} = 0 \text{ V}, V_{DS} = 650 \text{ V}$    |     |     |     |      |

#### **DYNAMIC CHARACTERISTICS**

| DINAMIC CHARACTERISTICS        |                     |                                                  |     |     |     |      |

|--------------------------------|---------------------|--------------------------------------------------|-----|-----|-----|------|

| PARAMETER                      |                     | CONDITIONS                                       | MIN | TYP | MAX | UNIT |

| Output Capacitance             | Coss                | $V_{DS} = 400 \text{ V}, V_{GS} = 0 \text{ V}$   |     | 14  |     | pF   |

|                                |                     | f = 100 kHz                                      |     |     |     |      |

| Output Charge                  | Qoss                | $V_{DS} = 400 \text{ V}, V_{GS} = 0 \text{ V}$   |     | 14  |     | nC   |

| Total Gate Charge <sup>3</sup> | Q <sub>G</sub>      | $V_{DS} = 400 \text{ V}, V_{GS} = 012 \text{ V}$ |     | 1.4 |     | nC   |

|                                |                     | I <sub>D</sub> = 2.75 A, I <sub>G</sub> =15 mA   |     |     |     |      |

| Reverse Recovery Charge        | Q <sub>RR</sub>     | $I_S = 8 \text{ A}, V_{DS} = 400 \text{ V}$      |     | 0   |     | nC   |

| Turn-on delay time             | t <sub>d(on)</sub>  | See Figure 17 and Figure 18                      |     | 5   |     | ns   |

| Turn-off delay time            | t <sub>d(off)</sub> | See Figure 17 and Figure 18                      |     | 13  |     | ns   |

| Rise time                      | t <sub>r</sub>      | See Figure 17 and Figure 18                      |     | 4   |     | ns   |

| Fall time                      | t <sub>f</sub>      | See Figure 17 and Figure 18                      |     | 4   |     | ns   |

\_

<sup>&</sup>lt;sup>3</sup> Turn-on gate charge value is listed. Turn-off gate charge value is lower, because ICeGaN™ gate discharges the gate internally.

Datasheet 1.0 – December 2022

#### **CURRENT SENSING**

Please refer to the application note CG-AN2206: Current Sensing with ICeGaN™. Please contact CGD for advice on the use of the current sense function.

#### **ESD RATING**

| PARAMETER                |  | CONDITIONS              | MIN  | TYP | MAX | UNIT |

|--------------------------|--|-------------------------|------|-----|-----|------|

| ESD withstand rating HBM |  | Human Body Model        | 2000 |     |     | V    |

|                          |  | (per JEDEC JS-001-2017) |      |     |     |      |

#### **Thermal Characteristics**

Typical values unless otherwise specified.

| PARAMETER                            |                     | CONDITIONS | VALUE | UNIT |

|--------------------------------------|---------------------|------------|-------|------|

| Thermal resistance, junction to case | R <sub>th(JC)</sub> |            | 2.5   | °C/W |

| Maximum reflow soldering temperature | T <sub>reflow</sub> | MSL 1      | 260   | °C   |

#### **Figures**

Figures at  $T_J = 25$  °C,  $V_{DD} = 12$  V if not specified.

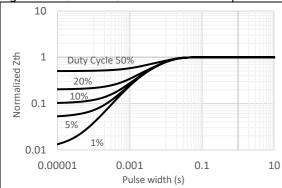

Figure 3. Normalized thermal transient impedance ( $Z_{th,JC}$ ) as a function of pulse width.

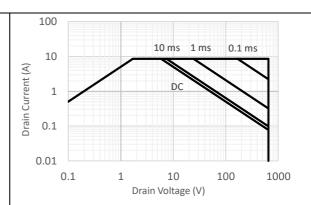

Figure 4. Safe Operating Area (SOA) based on thermal impedance  $Z_{th,JC}$  at  $T_{CASE} = 25$  °C.

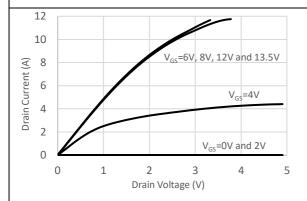

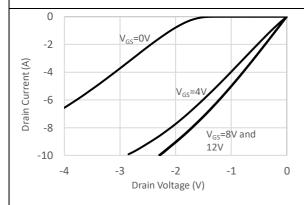

Figure 5. Forward output characteristics at  $T_J = 25$  °C.

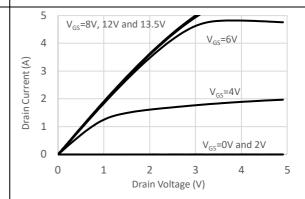

Figure 6. Forward output characteristic at  $T_J = 150$  °C.

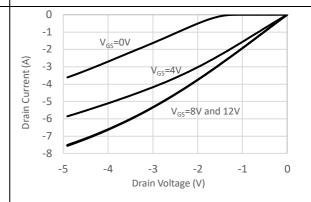

*Figure 7. Reverse output characteristics at T*<sub>J</sub> = 25 °C.

Figure 8. Reverse output characteristics at  $T_J = 150$  °C.

Figure 9. Drain leakage current characteristics at  $T_J = 25$  °C and  $T_J = 150$  °C.

Figure 10. On-state resistance as a function of drain current at  $T_J = 25$  °C.

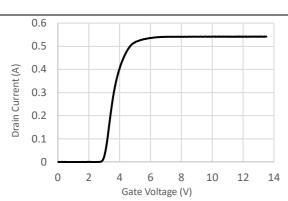

Figure 12. Transfer characteristics at  $V_{DS} = 0.1 \text{ V}$ ,  $T_{J} = 25 \text{ }^{\circ}\text{C}$ .

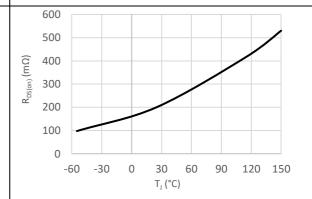

Figure 11. On-state resistance as a function of junction temperature at  $V_{GS} = 12 V$ .

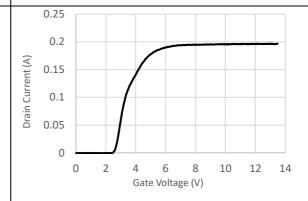

Figure 13. Transfer characteristics at  $V_{DS} = 0.1 V$ ,  $T_J = 150 \, ^{\circ}C.$

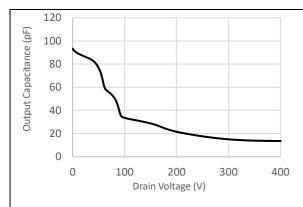

Figure 14. Typical output capacitance Coss vs. VDs at 100 kHz,  $T_{J} = 25 \, {}^{\circ}\text{C}.$

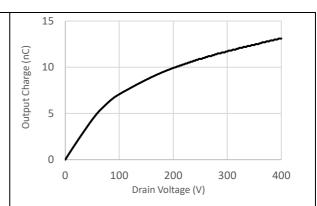

Figure 15. Typical output charge Qoss vs. VDs at 100 kHz,  $T_{J} = 25 \, ^{\circ}\text{C}.$

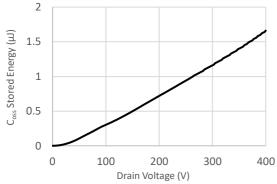

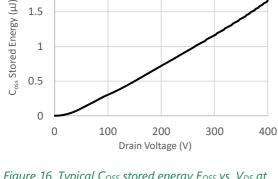

Figure 16. Typical Coss stored energy Eoss vs. V<sub>DS</sub> at  $T_J = 25$  °C.

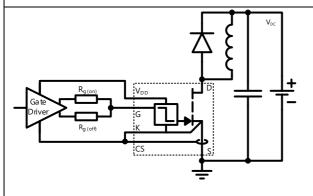

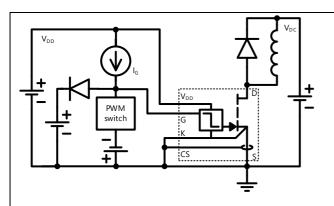

Figure 17. Inductive switching circuit.  $I_D = 6$  A,  $R_{g(on)} = 15 \Omega$ ,  $R_{g(off)}=2~\Omega,~V_{DD}=12~V,~V_{DC}=400~V,~L=125~\mu H,$ diode = IDH04G65C5.

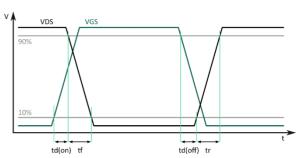

Figure 18. Switching waveform timing definitions.

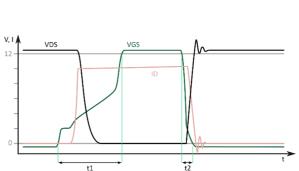

Figure 19.  $Q_G$  gate charge characterization circuit.  $I_G$ =15 mA,  $V_{DC}$  = 400 V,  $V_{DD}$ =12V, L = 125  $\mu$ H, freewheeling diode = IDH04G65C5.

Figure 20.  $Q_G$  gate charge characterisation waveform at  $I_G = 15$  mA and  $V_{DD} = 12$  V. Time intervals t1 and t2 indicate the integration boundaries to calculate  $Q_G$  from  $I_G$  at turn-on and turn-off. Turn-off gate charge is lower than turn-on gate charge.

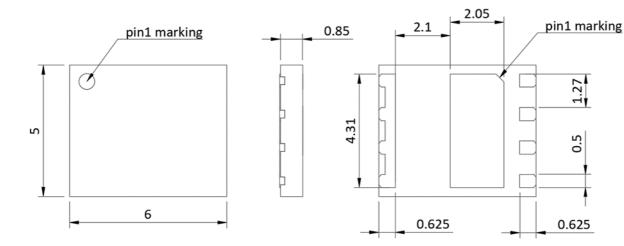

#### **Packaging**

DFN 5x6 mm.

| PIN NUMBER | NAME            |  |

|------------|-----------------|--|

| 1          | Kelvin Source   |  |

| 2          | Gate            |  |

| 3          | Current Sense   |  |

| 4          | V <sub>DD</sub> |  |

| 5-8        | Drain           |  |

| 9          | Source          |  |

Like any unwanted electronic device, CGD components should be recycled or otherwise disposed of in accordance with local laws and regulations.

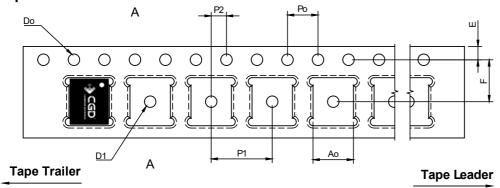

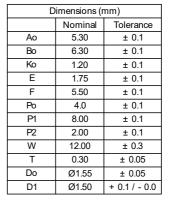

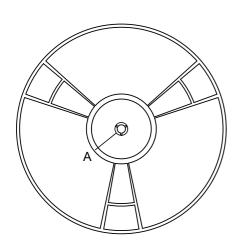

#### **Tape and Reel Information**

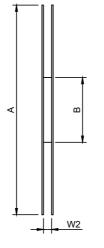

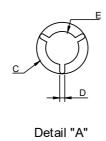

Detailed "A-A"

Tape Trailer - a minimum length of 160mm empty cavities sealed with cover tape. Tape Leader - a minimum length of 400mm empty cavities sealed with cover tape.

Isometric View

W1

| 13" Reel Dimensions (mm) |       |       |  |  |  |  |

|--------------------------|-------|-------|--|--|--|--|

| Min Max                  |       |       |  |  |  |  |

| W1                       |       | 18.2  |  |  |  |  |

| W2                       | 12.3  | 13.1  |  |  |  |  |

| Α                        | 328.0 | 332.0 |  |  |  |  |

| В                        | 100.0 | 104.0 |  |  |  |  |

| С                        | 20.2  |       |  |  |  |  |

| D                        | 1.5   | 2.5   |  |  |  |  |

| Е                        | 12.8  | 13.5  |  |  |  |  |

#### **Version History**

This version is 1.0

| THIS VERSION IS 1.0 |                 |               |            |  |  |  |

|---------------------|-----------------|---------------|------------|--|--|--|

| VERSION             | DESCRIPTION     | DATE          | ВУ         |  |  |  |

| 1.0                 | Initial Release | December 2022 | MA, AB, JZ |  |  |  |

### Dare to innovate differently

Cambridge GaN Devices Limited Jeffreys Building, Suite 8 St John's Innovation Park Cambridge CB4 0DS

#### Disclaimer

Information presented here by Cambridge GaN Devices Limited is believed to be correct and accurate. Cambridge GaN Devices Limited shall not be liable to any recipient or third part for any damages, including (but not limited to) personal injury, property damage, loss of profits, loss of business opportunity, loss of use, interruption of business, or indirect, special, incidental or consequential damages of any kind in connection with, or arising from, the use or performance of the data herein.

No obligation or liability to the recipient or third part shall arise from Cambridge GaN Devices Limited providing technical or other services. CGD reserves the right to modify the products and/or specifications described herein at any time and at Cambridge GaN Devices' sole discretion. All information in this document, including descriptions of product features or performance, is subject to change without notice.