- Original content, please do not reprint.

The story on this subject begins with these two criteria.

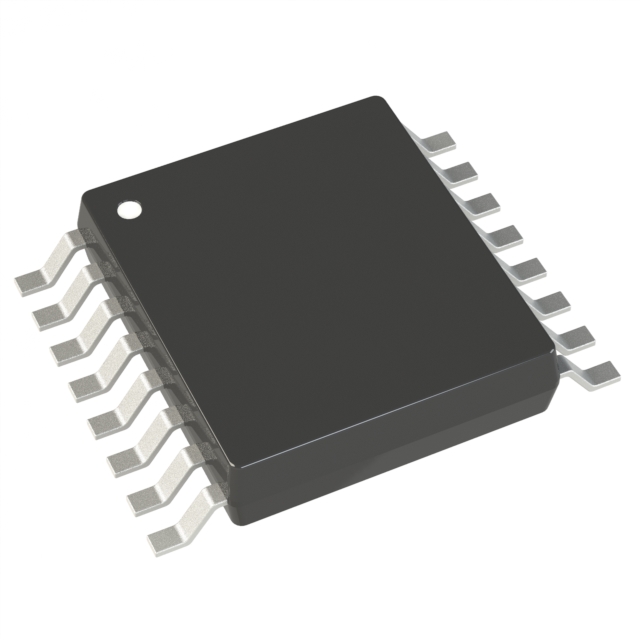

• EDEC (Joint Electronic Equipment Engineering Council) and EIAJ (Electronic Machinery Industry Association of Japan), different manufacturers follow two different standards, either separately or at the same time. As a result, there are three branch concepts of "wide body, medium body, and narrow body", which confuses many people.

• Let's start with the source. EIAJ is often used to use SOPs. JEDEC is commonly used to use SOICs. In fact, SO is =SOP=SOIC. Knowing this, the remaining question is volume.

• EIAJ typically uses SOP (5.3mm body width) and JEDEC typically uses SOIC (3.9mm and 7.5mm body width). It would be nice if everyone chose a standard to implement, but some manufacturers prefer to use both standards. Implementation results in a mix of these two standards. This makes the already chaotic situation even more chaotic.

It is also SOP8 encapsulated. The JEDEC standard is 3.8*6.0mm, and the EIAJ is 5.3*7.9mm. Among them, the SOP-16 JEDEC standard is 3.8*6.0 and 7.2*10.2.

My friend said that the data is hard to remember. Actually, it's not that difficult, as long as you memorize a few volumes.

The narrow body width is 3.9mm, the middle body width is 5.2mm, and the wide body width is 7.2mm.

It is the standard model that the engineer uses when designing the volume that determines it, which leads to which standard must be used for subsequent procurement.

Friends who buy chips may ask, every time you buy a chip, you have to confirm with both parties what is narrow, medium or wide, is it so troublesome? The good news is that this chaos mostly occurs in the 74 series of digital logic chips. It only needs to distinguish between the types of chips that are easily confused in the packaging standard. The standards for other types of chips on the market are relatively consistent.